Chip Gallery

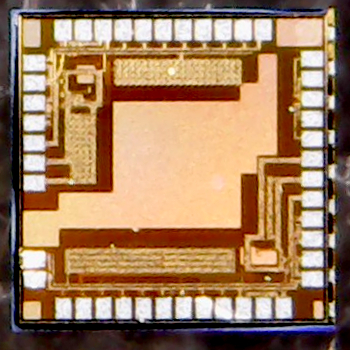

Analog to digital interface circuit for a relative humidity SAW sensor

|

Analog to digital interface circuit for a relative humidity SAW sensor |

1-GHz CMOS Differential Ring Oscillator (research project – 2017)

1-GHz CMOS Differential Ring Oscillator (research project – 2017)

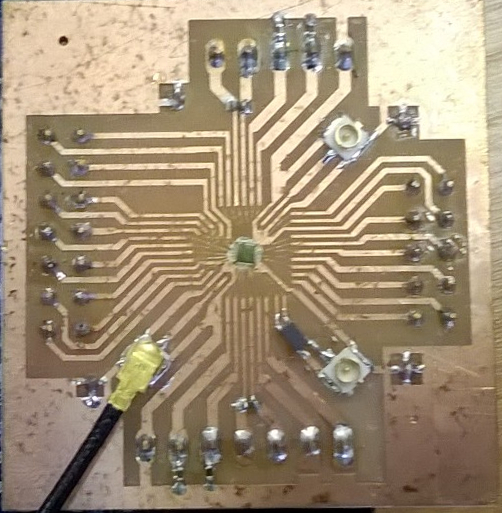

HBC Transceiver (student project 2016/2017)

|

Photo of the HBC Transceiver

(packaged chip assembled in a PCB)

(photo of the die)

|

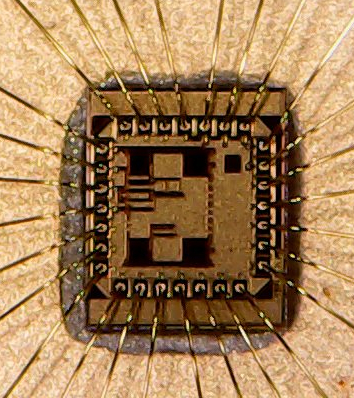

High Frequency LC parameter extractor (student project 2016/2017)

|

Photo of the LC parameter extractor

assembled on a PCB (wirebonding)

|

Double Feedback Oscillator (student project 2015/2016)

|

Double Feedback Oscillator.

|

Class-E Power Amplifier (student project 2016)

|

Class-E Power Amplifier.

|

25-dBm 1-GHz Class-D Power Amplifier (student project 2015)

|

25-dBm 1-GHz Power Amplifier.

|

Fully-integrated Tag with Digital Memory (student project 2016)

|

Fully-integrated Tag with Digital Memory.

|

CMOS fully-integrated receiver for medical implants (student project 2015)

|

A CMOS fully-integrated receiver for autonomous implanted devices.

|

Automatic test and correction of LC resonator (student project 2015)

|

The correction of the LC resonance frequency is done with an ultra-fast a simple circuit based on high dynamic range negative-resistance circuit.

|

Conditioning circuit for ISFET-based sensor (research project 2014)

400 MHz Superregenerative receiver (research project 2014)

|

400 MHz superregenerative receiver for WBAN applications.

|

2.4 GHz CMOS Hartley oscillator (student project 2013)

|

Ultra-low power CMOS oscillator based on the Hartley topology. This project was developed by graduate students as an assignment of the Radio Frquency Electronics course

|

900 MHz UHF Energy harvester (research project 2012)

|

This 900 MHz UHF Energy harvester is going to be used for powering a WBAN temperature sensor.

|

|

A Duty-Cycle Controlled Variable-Gain Amplifier for WBAN applications (student project 2012)

Low Voltage LNA (student project 2012)

Low Power LNA (student project 2012)

A 2.4GHz Cascode CMOS Low Noise Amplifier (student project 2012)

2.4 GHz Ultra Low-Voltage Oscillator (research project 2012)

Low-voltage Super-regenerative receiver at 2.4GHz ( 2012).